## Comparative Analysis of Array Multiplier Using Different Logic Styles

# M.B. Damle, Dr. S.S Limaye, M.G. Sonwani<sup>2</sup>

Electronics Engineering Department, RCOEM, Nagpur (MH), India Electronics Engineering Department, JIT, Nagpur (MH), India

*Abstract:* Multiplier is one of the most important arithmetic unit in Microprocessors and DSPs and also a major source of power dissipation. Reducing the power dissipation of multipliers is a key to satisfy the overall power budget of various digital circuits and systems. this paper elaborates the array multiplier through different logic styles. The fundamental units to design a multiplier are adders. The various types of adders used in this paper are complementary MOS (CMOS)logic style, complementary pass-transistor (CPL) logic style, double-pass transistor (DPL) logic style and domino logic style. The main objective of our work is to calculate the average power, delay and PDP of 4x4 multipliers. The design of full adder for low power is obtained and the low power units are implemented on the array multiplier and the results are analyzed for better performance. The designs are done using TANNER S-EDIT tool and are simulated using T-SPICE. The multiplier architectures are designed using the three better above said full adders and the results are compared so that we can obtain a better multiplier design.

Keywords: Array Multipliers, Full adder, CMOS, CPL, DPL, Domino Logic power delay product.

## I. INTRODUCTION

The core of every microprocessor, digital signal processor (DSP), and data processing application like specific integrated circuit (ASIC) is its data path. At the heart of data-path and addressing units in turn are arithmetic units, such as comparators, adders, and multipliers. Finally, the basic operation found in most arithmetic components is the binary addition. Computations needs to be performed using low-power, area-efficient circuits operating at greater speed. Addition is the most basic arithmetic component of the processor.

The rest of the paper is organized as follows. Section II describes the different logic styles. Section III elaborates the array multiplier. Section IV and V are followed by simulation results and conclusion.

#### II. LOGIC STYLES

Ila Gupta et al. has proposed a large number of CMOS logic design styles [5]. For multiplication, adder is used as a basic element. For arithmetic applications, following three different logic styles are used for a full adder design to achieve best performance results for multiplier design [6].

#### A. Conventional Static CMOS-CSL

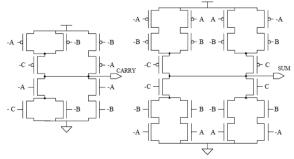

The recent VLSI arithmetic applications [6] i.e 4-bit RCA, uses conventional static CMOS logic. The schematic diagram of a conventional static CMOS full adder cell is illustrated in figure 1.

Fig 1: CSL Logic Full adder

The signals noted with '-' are the complementary signals. The p- MOSFET network of each

stage is the dual network of the n- MOSFET. Advantages of the CMOS logic style are its robustness against voltage scaling and transistor sizing (high noise margins) and thus reliable operation at low voltages and arbitrary (even minimal) transistor sizes (ratio less logic).

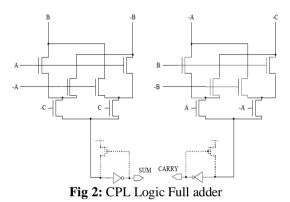

#### B. Complementary Pass Transistor Logic-CPL

The basic difference of pass-transistor logic compared to the CMOS logic style is that the source side of the logic transistor networks is connected to some input signals instead of the power lines. The advantage is that one pass-transistor network (either NMOS or PMOS) is sufficient to perform the logic operation, which results in a smaller number of transistors and smaller input loads, especially when NMOS networks are used.CPL [7] uses only an n-MOSFET network for the implementation of logic functions, thus resulting in low input capacitance and high-speed operation [8]. The schematic diagram of the CPL full adder circuit is shown in figure 2. Because the high voltage level of the pass-transistor outputs is lower than the supply voltage level by the threshold voltage of the pass transistors, the signals have to be amplified by using CMOS inverters at the outputs [9]. The advantages [10] of pass logic transistors include – Smaller number of transistors and smaller input loads, along with MUX and especially XOR circuits being implemented efficiently. The disadvantage [10] of pass transistor logic is that threshold voltage drops through the NMOS transistors makes it necessary to maintain output voltage level; hence inverter is used at output which increases the number of transistors.

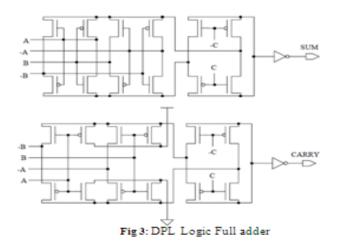

C. Double Pass Transistor Logic-DPL

DPL [11][12] is a modified version of CPL. The circuit diagram of the DPL full adder is given in figure 3. In DPL circuit full swing operation is achieved by simply adding p- MOSFET transistors in parallel with the n-MOSFET transistors. Hence, the problems of noise margin and speed degradation at reduced supply voltages, which are caused in CPL circuits due to the reduced high voltage level, are avoided.

The basic difference of pass-transistor logic compared to the CMOS logic style is that the source side of the logic transistor networks is connected to some input signals instead of the power lines. The advantage is that one pass-transistor network (either NMOS or PMOS) is sufficient to perform the logic operation, which results in a smaller number of transistors and smaller input loads, especially when NMOS networks are used. However, the threshold voltage drop (Vout = Vdd - Vtn) through the NMOS transistors while passing

logic "1" makes swing (or level) restoration at the gate outputs necessary in order to avoid static currents at the subsequent output inverters or logic gates

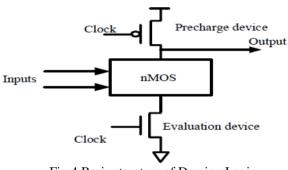

#### D. Domino Logic

Domino logic circuits have many advantages such as high speed of operation, minimum used area, low noise margins, and the most important of all, they offer potential power consumption savings since the overall gate capacitance is smaller than their static counterparts [21-25]. For this reason circuit design using domino logic tends to be a very attractive method for high performance, low-power designs.

The basic structure of domino logic is shown in Fig. 4. It is a non-inverting structure, and consists of a nMOS transistor network, which implements the required logic function, two transistors (an *nMOS* and a PMOS) where the clock signal is applied and synchronizes the operation of the circuit, and a static CMOS inverter which provides the circuits output.

Fig.4 Basic structure of Domino Logic

The period where CLK is low is called the precharge phase. In this phase the internal node, F is charged to power supply voltage while the output node, F, is discharged to ground. The period where CLK is high is called the evaluation phase. In this phase the values of the inputs determine the discharge (F = 0) or not (F = 1) of the internal node The inverter in the output of a domino logic circuit is included for several reasons. First, it is required for proper operation of a chain of domino gates. Second, the internal node F is a weak node, when the clock is high, the high value on that node is not driven [8].

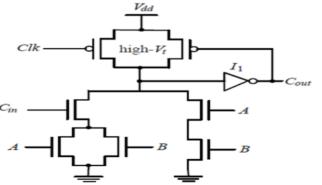

Fig. 5 shows the schematic of the CARRYOUT circuit. The core of this circuit is the domino logic that implements the function of CARRYOUT[9]. This circuit will stay in standby phase when the clock signal CLK is "logic 1. It will turn in the evaluating phase if the clock signal CLK is "logic 0. For the high-speed operation, the inverter I1 is designed in multi- threshold methodology where a low-Vt PMOS transistor is connected with a high-Vt NMOS transistor such that the logic 0 can pass the inverter at a higher speed.

Fig.5: CARRYOUT Circuit Domino Logic AND Gate

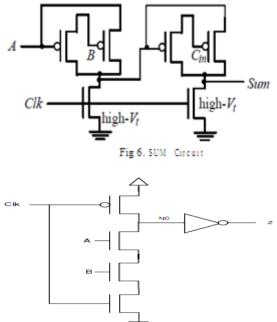

The Circuit for SUM Operation Fig. 6 shows the schematic of the SUM circuit. The SUM circuit is composed of two XOR gates. The XOR gate is modified from the cross-coupled version by replacing the NMOS portion with a clock gated NMOS. In this circuit, the PMOS transistors receive the input signal A, B, and Cin. The operation of this circuit can be divided into two phases: the IDLE PHASE and the EVALUATING PHASE. In the IDLE PHASE, the clock signal CLK is "logic 1, and the output signal SUM will be "logic 0. In the EVALUATING PHASE, the clock signal CLK is

"logic 0, and the corresponding output signal SUM will be evaluated according to the input signals A, B, and Cin.

Fig.7: 2 input AND Gate using Domino Logic

#### III. ARRAY MULTIPLIER

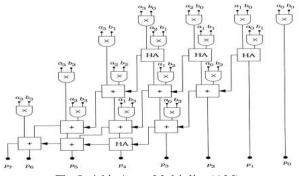

An array multiplier is very regular in structure as shown in figure 4. It uses short wires that go from one full adder to adjacent full adders horizontally, vertically or diagonally [13]. An  $n \times n$  array of AND gates can compute all the *i i a b* terms simultaneously. The terms are summed by an array of 'n [n - 2]' full adders and 'n' half adders. The shifting of partial products for their proper alignment is performed by simple routing and does not require any logic. The number of rows in array multiplier denotes length of the multiplier and width of each row denotes width of multiplicand. The output of each row of adders acts as input to the next row of adders. Each row of full adders or 3:2 compressors adds a partial product to the partial sum, generating a new partial sum and a sequence of carries.

Fig 8: 4-bit Array Multiplier (AM)

The delay associated with the array multiplier is the time taken by the signals to propagate through the AND gates and adders that form the multiplication array. Delay of an array multiplier depends only upon the depth of the array not on the partial product width. The delay of the array multiplier is given by [14]:

$$(T \ critical) = [(N - 1) + (N - 2)] T(Carry) + (N - 1)T(Sum) + T(AND)$$

3)

ere T (*Carry*) is the propagation delay between input and output carry, T (*Sum*) is the delay between the input carry and sum bit of the full adder, T (*AND*) is the delay of AND gate, N is the length of

multiplier operand. The advantage of array multiplier is its regular structure. Thus it is easy to layout and has small size. In VLSI designs, the regular structures can be tiled over one another. This reduces the risk of mistakes and also reduces layout design time. This regular layout is widely used in VLSI math coprocessors and DSP chips [15].

#### IV. SIMULATION RESULT

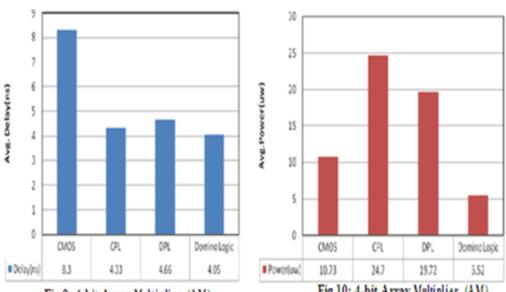

The 4-bit multipliers are compared based on the performance parameters like propagation delay, and power dissipation. To achieve better performance, the circuits are designed using CMOS process by MOSIS in 180 nm technology. All the circuits have been designed using TANNER EDA[16].

Table I Comparative analysis of Array Multiplier Using Different Logic Style Full Adder

|             | 1         |           |         |

|-------------|-----------|-----------|---------|

| Logic Style | Delay(ns) | Power(uw) | PDP(FJ) |

| CMOS        | 8.30      | 10.73     | 89.06   |

| CPL         | 4.33      | 24.70     | 131.82  |

| DPL         | 4.66      | 19.72     | 92.03   |

| Domino      | 4.05      | 5.52      | 22.35   |

www.iosrjen.org

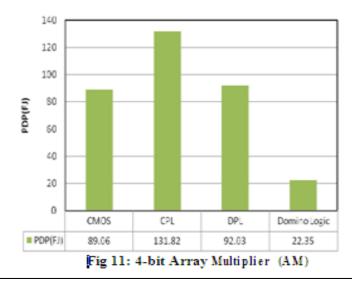

Table I shows the simulation result of 4x4 array multipliers through different logic styles, similarly figure 9, figure 10 and figure 11 shows the delay power and PDP of different logic style array multiplier respectively. Figure 10 shows the minimum power dissipation for Domino logic while maximum power dissipation for CPL based array multiplier.

#### V. CONCLUSION

It has been observed that Domino logic design style exhibit better characteristics (speed and power) as compared to other design styles. So, Domino logic style can be used where power and high speed is the prime aim. Where, Domino logic

consumes the lowest power among the four. so Domino logic can be considered best logic design style with respect to all parameters of 4-bit array multiplier architectures as shown in Table I.

#### VI. ACKNOWLEDGMENT

The authors would like to thank RCOEM Nagpur, India. This work has been done in VLSI design and simulation laboratory at Ramdeobaba College of Engineering and Management Nagpur (MH), INDIA.

### REFERENCES

- [1].

- Chandrakasan, R. Brodersen, "Low Power Design", Kluwer Academic Publishers, 1995. Z. Turker,, S. P.Khatri , "A DCVSL Delay Cell for Fast Low Power Frequency Synthesis [2]. Applications", IEEE transactions on circuits and systems June 2011, vol. 58, no. 6, pp. 1125-1138.

- T. Sharma, Prof. B.P.Singh, K.G.Sharma, N. Arora , "High Speed Array Multipliers Based on 1-Bit [3]. Full Adders", in Int. J. of Recent Trends in Engineering and Technology, Vol. 4, No. 4, pp.26-28, Nov 2010.

- Gupta, Neha Arora, Prof.B.P.Singh, "Simulation and Analysis of 2:1 Multiplexer [4]. Circuits at 90nm Technology" in International Journal of Modern Engineering Research, Vol.1, Issue.2, pp-642-647, ISSN: 2249-6645, 2011.

- Ila Gupta, Neha Arora, Prof.B.P.Singh, "Low Power 2:1 Multiplexer Design Using DCVS Logic [5]. and Its Application in 1-Bit Full Adder Cell" in International Conference on Electronics and Communication Engineering (ICECE), March 03, 2012, Bhopal, India.

- J. T. Yan and Z. W. Chen, "Low-power multiplier design with row and column bypassing", IEEE [6]. International SOC Conference, pp.227-230, 2009.

- Bellaouar, A., and Elmasry, M. I., Low-Power Digital VLSI Design: Circuits and Systems, Kluwer, [7]. Norwell, MA, 1995.

- Parhami, B., "Computer Arithmetic -Algorithms and Hardware Designs", Oxford University Press, 2000. [8].

- Rabaey, J.M., Chandrakasan, A., and Nikolic, B.,"Digital Integrated Circuits", Second Edition, PHI [9]. Publishers, 2003.

- Ware, F.A., McAllister, W.H., Carlson, J.R., Sun, D.K., and Vlach, R.J., "64 Bit onolithicFloating [10]. Point Processors", IEEE Journal of Solid-State Circuits, vol. 17, no. 5, pp. 898-90, October 1982.

- [11]. Parhami, B., Computer Arithmetic Algorithms and Hardware Designs, Oxford University Press, 2000.

- [12]. J.M., Chandrakasan, A., and Nikolic, B., Digital Integrated Circuits, Second Edition, PHI Publishers, 2003

- [13]. Ware, F.A., McAllister, W.H., Carlson, J.R., Sun, D.K., and Vlach, R.J., 64 Bit Monolithic Floating Point Processors,

- IEEE Journal of Solid-State Circuits, vol. 17, no. 5, October 1982, pp. 898-90. [14].

- C.S. Wallace, A suggestion for a fast multiplier, in IEEE Trans. On Electronic Computers, vol. EC-[15]. 13, 1964, pp. 14-17.

- P. M. Kogge and H. S. Stone, A Parallel Algorithm for the Efficient Solution of a General Class of [16]. Recurrence Equations,

- IEEE Transactions on Computers, vol. 22, no. 8, August 1973, pp. 786–793. [17].

- Tanner EDA Inc. 1988, User s Manual, 2010. [18].

- A survey of power estimation techniques in VLSI circuits, IEEE Transactions on VLSI Najm, F., [19]. Systems, vol. 2, 1995, pp. 446-455.

- Kang, S., Accurate simulation of power dissipation in VLSI circuits, IEEE Journal of Solid-State [20]. Circuits, vol. 21, 1986, pp. 889-891.

- G. E. Sobelman and D. L. Raatz, "Low-Power Multiplier Design Using Delayed Evaluation", in Proc. [21]. of IEEE International Symposium on Circuits and Systems, pp. 1564-1567, 1995.

- Weste, and K. Eshraghian, "Principles of CMOS VLSI Design", Addison-Weslet Publishing [22]. Company, 1992.

- [23]. J. H. Satyanarayana and K. K. Parhi, "A Theoretical Approach to Estimation of Bounds on Power Consumption in Digital Multipliers", *IEEE Trans. on Circuits and Systems II, vol. 44, no.* 6, pp. 473-481, June 1997.

- [24]. C. Farnsworth, D. A. Edwards and S.S. Sikand, Utilising Dynamic Logic for Low Power Consumption in Asynchronous Circuits", in *Proc. of IEEE ISARACS, Salt Lake City, Utah, USA,Nov.* 1994.

- [25]. D. V. Campenhout, T. Mudge and K. Sakallah, "Timing Verification of Sequential Domino Circuits," in *Proc. of IEEE/ACM International Conference on Computer-Aided Design*, pp. 127-132, 1996

- [26]. J. M. Rabaey, M. Pedram, "Low Power Design Methodologies", Kluwer Academic Publishers, 1996.

- [27]. D. V. Campenhout, T. Mudge and K. Sakallah, "Timing Verification of Sequential Domino Circuits," in *Proc. of IEEE/ACM International Conference on Computer-Aided Design*, pp. 127-132, 1996

- [28]. Chuen-Yau Chen and Yung-Pei Chou "Novel Low-Power 1-bit Full Adder Design" 2009 IEEE

## Biography

- (1) M.B.Damle, Associate Professor, RCOEM, Nagpur, M.S. from BITS PILANI RAJASTHAN, SMIEEE, FIETE, CE (IE)

- (2) Dr.S.S.Limaye, Ph.D. Electronics, Principal, Zhulelal C.O.E. Nagpur. SMIEEE, FIETE, CE (IE)

- (3) M.G.Sonwani ,Assistant Professor, RCOEM ,Nagpur, M Tech from National Institute of Technology ,Hamirpur ,India.